Videos

This video is a demo of how to use the Timeline in the FS2800 when data has been captured.

This is a short video that shows how to use the FS4500 DisplayPort Protocol Analyzer to recognize an event on the Aux Channel, trigger, and then trigger the high speed main link.

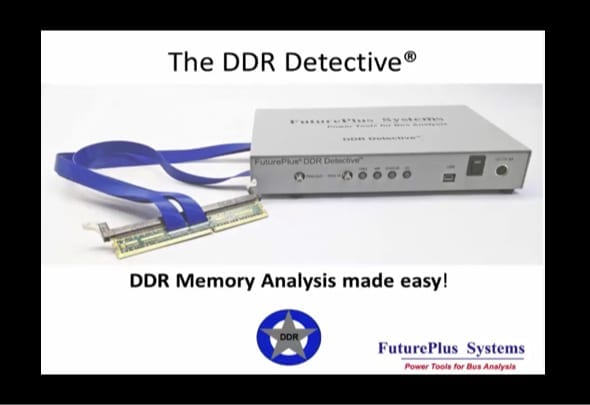

This quick video gives a detailed step by step view of how to quickly setup the DDR Detective using the automated Setup Wizard.

This ‘how to’ video describes how to use the FS2800A DDR Detective’s 2D (voltage and time) Eye Detector.

Listen to Greg Moser of FuturePlus Systems demonstrate the FS4500 DisplayPort Protocol Analyzer on a REAL DisplayPort Link.

This video shows how the Pixel Renderer software works.

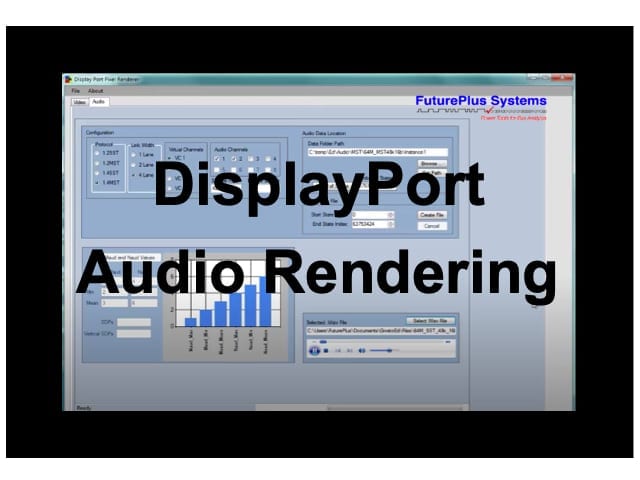

This quick video is an updated look at our Github available Audio Rendering Tool.

The DDR Detective is the most cost effective tool for analyzing DDR Memory. It can analyze DDR3, DDR4, LPDDR3 AND LPDDR4.

Short DisplayPort Tutorial on the various packets on the High Speed Main Link. The FS4500 DisplayPort Protocol Analyzer is used to show real link traffic.

The only tool you will need to debug and validate all the DisplayPort versions and speeds up to and including HBR3!

This video is a quick overview of the DDR Detective from FuturePlus Systems. DDR4, DDR3, LPDDR3 and LPDDR4 validation and performance verification done easy!

Join Emily Bender OSU Co-op student with FuturePlus Systems as she does a quick review of the signaling and commands for DDR4 memory.

Learn the key metrics for DDR4 memory performance. This video gives an overview of the DDR Detective Performance Analysis feature.

Watch the Google Row Hammer code run on a DDR3 based system. See how it creates excessive ACT commands to the DIMM using the DDR Detective Row Hammer event detection feature.

Presentations

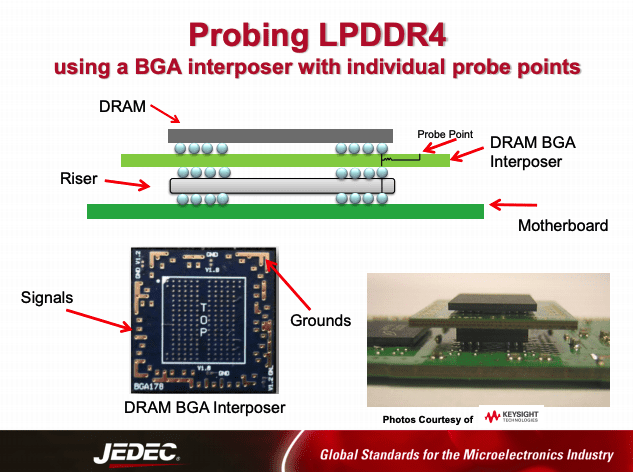

Get it right the first time! LPDDR4 Validation and Compliance Test.

Google Study: Could those memory failures be caused by design flaws? – Server Memory Forum Shenzhen 2012. Paper version.